타일링이란 모형을 관리 가능한 작업 구역으로 분리하는 것을 말합니다. 이 프로세스는 많은 양의 데이터 작업을 용이하게 하며 설계 팀에서 향상된 데이터 협업이 가능하게 합니다.

기존 지표면

큰 코리더 영역의 기존 지표면 모형을 도면당 하나의 타일을 사용하여 타일에서 작성할 수 있습니다. 타일 조합은 전체 프로젝트를 나타냅니다. 플롯 또는 분석을 위해 인접 지표면 영역을 함께 사용해야 할 경우 데이터 참조를 사용하여 해당 영역을 가져옵니다. 선형 설계의 경우 각 지표면 타일의 종단 지반선(EG)을 단일 종단 뷰로 결합하여 EG 종단의 연속 뷰를 표시합니다.

큰 단지 블록

모형 타일링의 개념은 큰 단지 블록을 다룰 때에도 효과적입니다. 설계자가 프로젝트의 여러 타일 또는 단계에서 동시에 작업할 수 있도록 로트 및 코리더 모형을 타일링할 수 있습니다.

코리더의 여러 영역

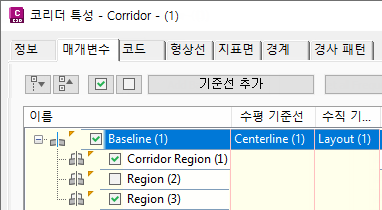

긴 코리더나 코리더 네트워크의 경우 모델링을 위해 여러 영역을 작성합니다. 일반적으로 코리더 영역은 한 표준횡단 사용이 끝나고 다른 표준횡단이 시작되는 위치에서 영역 경계가 발생할 때 서로 다른 표준횡단 사용을 표시하기 위해 사용됩니다. 그러나 표준횡단을 변경하지 않고 영역을 추가할 수도 있습니다. 추가 영역의 값은 제어가 가능합니다. 그림 13에서처럼 코리더 특성 대화상자를 사용하여 현재 작업에 필요하지 않은 영역의 모델링을 끌 수 있습니다. 이렇게 하면 코리더 재작성 속도가 향상됩니다.

그림 13: 코리더 영역 및 기준선 끄기

코리더에 지표면 또는 표준횡단의 변경이 적은 일부 영역이 있는 경우 이러한 영역의 코리더 모델링 빈도를 줄여 처리 속도를 향상시키는 것을 고려해 보십시오.