Beim Einrichten einer CFD-Simulation aus einem CAD-Modell können sich verschiedene Geometrieprobleme bei Bauteilen und Baugruppen negativ auf den Abschluss der Vernetzung oder die Netzqualität auswirken. Für Baugruppen bewertet das MAT drei geometrische Situationen und liefert Ihnen die Daten und Einstellungen der Ergebnisse als Hilfe für Ihre Prüfung. Verwenden Sie das MAT und Ihr technisches Urteilsvermögen, um die Bedeutung potenzieller Probleme zu bestimmen und Vorkehrungen für die Behebung der Probleme zu treffen. Stoßen Sie auf ein Problem, kehren Sie zur CAD-Anwendung zurück und ändern Sie die Geometrie entsprechend.

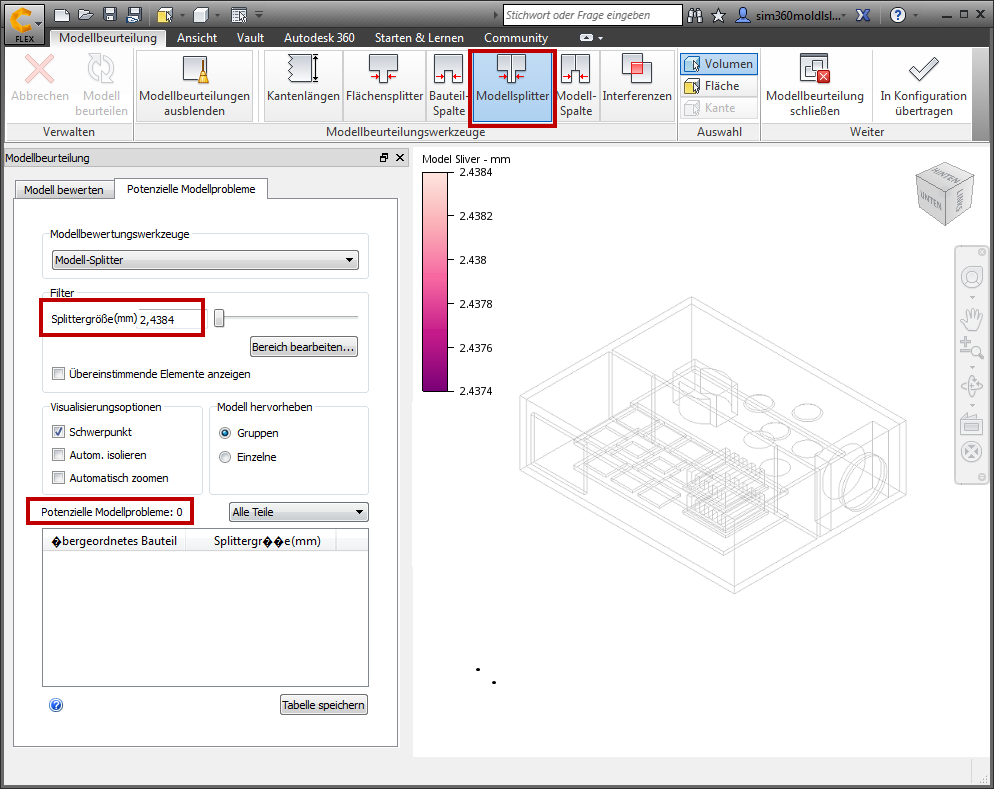

Modell-Splitter

Bauteile können so aneinander angrenzen, dass Flächen mit großen Aspektverhältnissen, sogenannte Splitterflächen, entstehen. Splitterflächen erfordern feine Netzknoten, was die Netzanzahl deutlich erhöhen kann. Außerdem können Splitterflächen zu einem unstetigen lokalen Verhalten der Netzlängenskala führen, was sich negativ auf die Lösungsgenauigkeit auswirkt. Verwenden Sie das Modell-Splitter-Werkzeug zur Prüfung Ihres Modells auf potenzielle Splitterflächenprobleme.

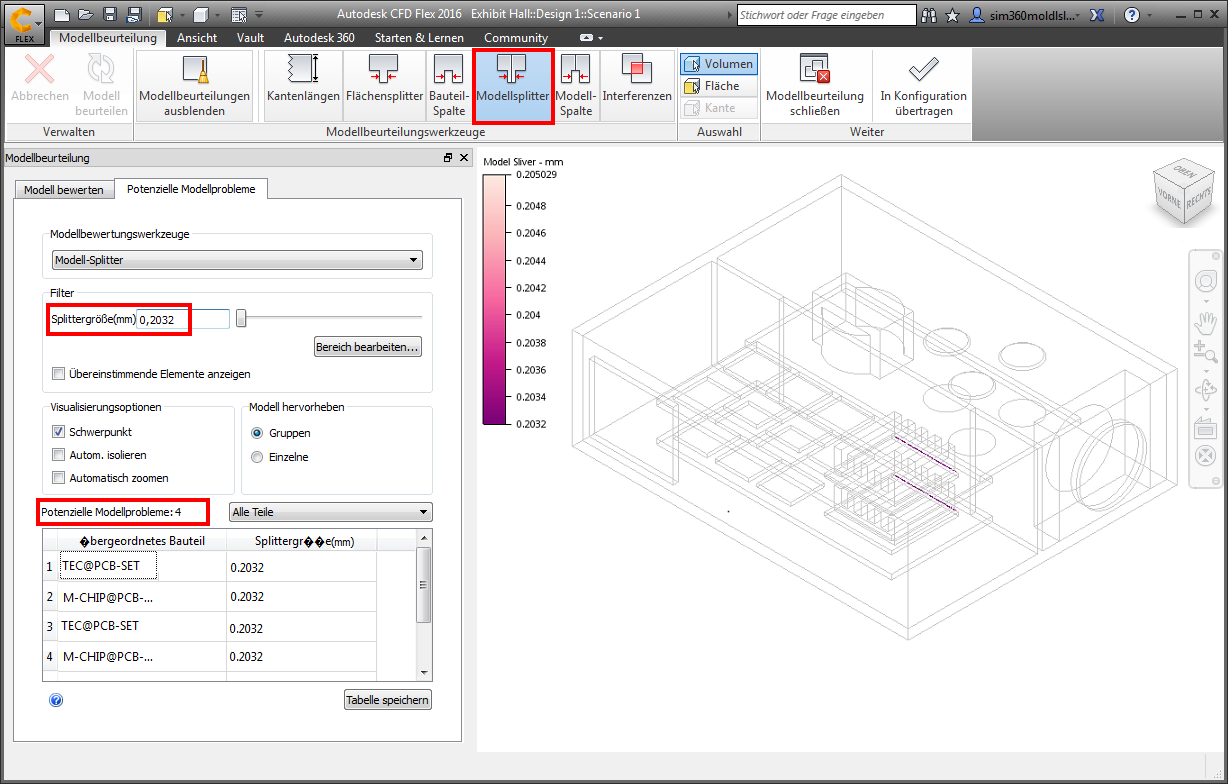

Die folgende Abbildung zeigt unser Elektronikgehäuse-Baugruppenmodell bei aktivem Modell-Splitter-Werkzeug. Die Ausgangseinstellung für den Splittergrößen-Filter beträgt vorgabemäßig 0.2032 mm, was vier potenzielle Splitterprobleme liefert.

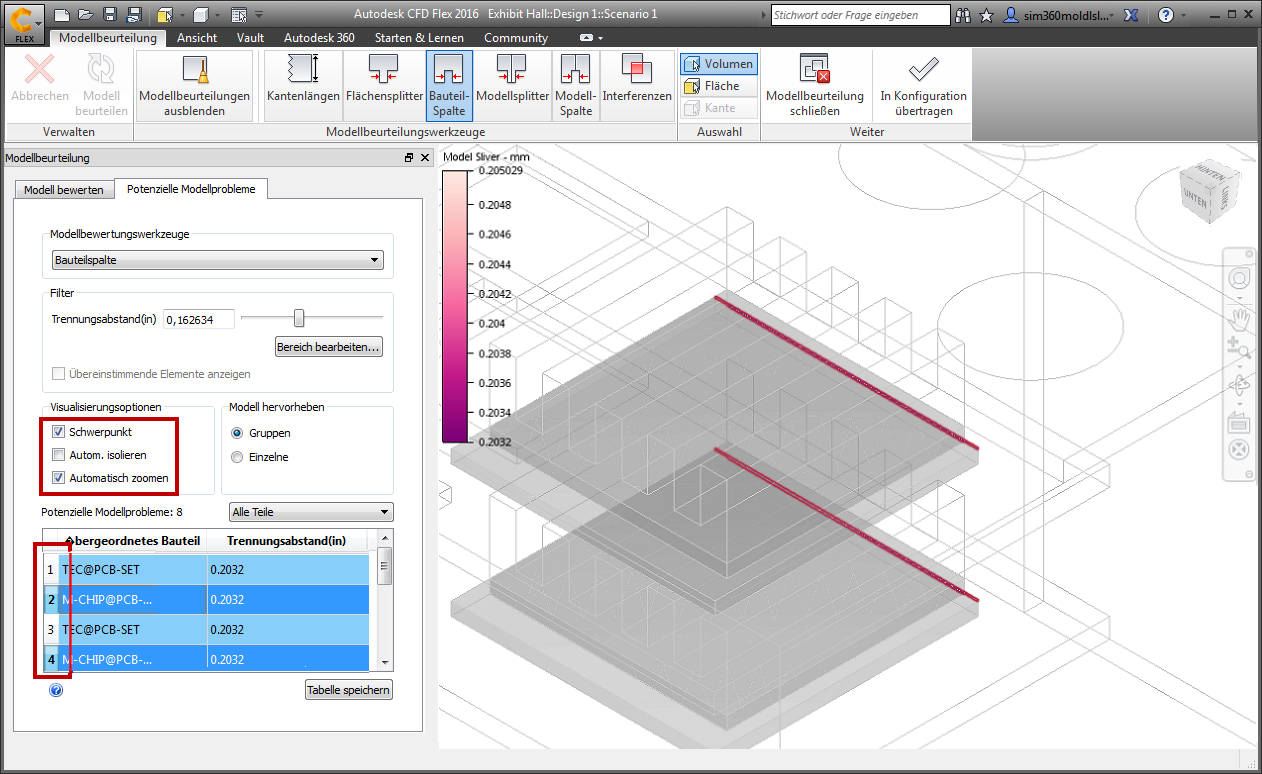

Wenn Sie die Tabelleneinträge und anschließend Automatisch Zoomen und Schwerpunkt wählen, werden die potenziellen Splitterprobleme an den Schnittstellen zwischen den Chips und Kühlkörpern angezeigt.

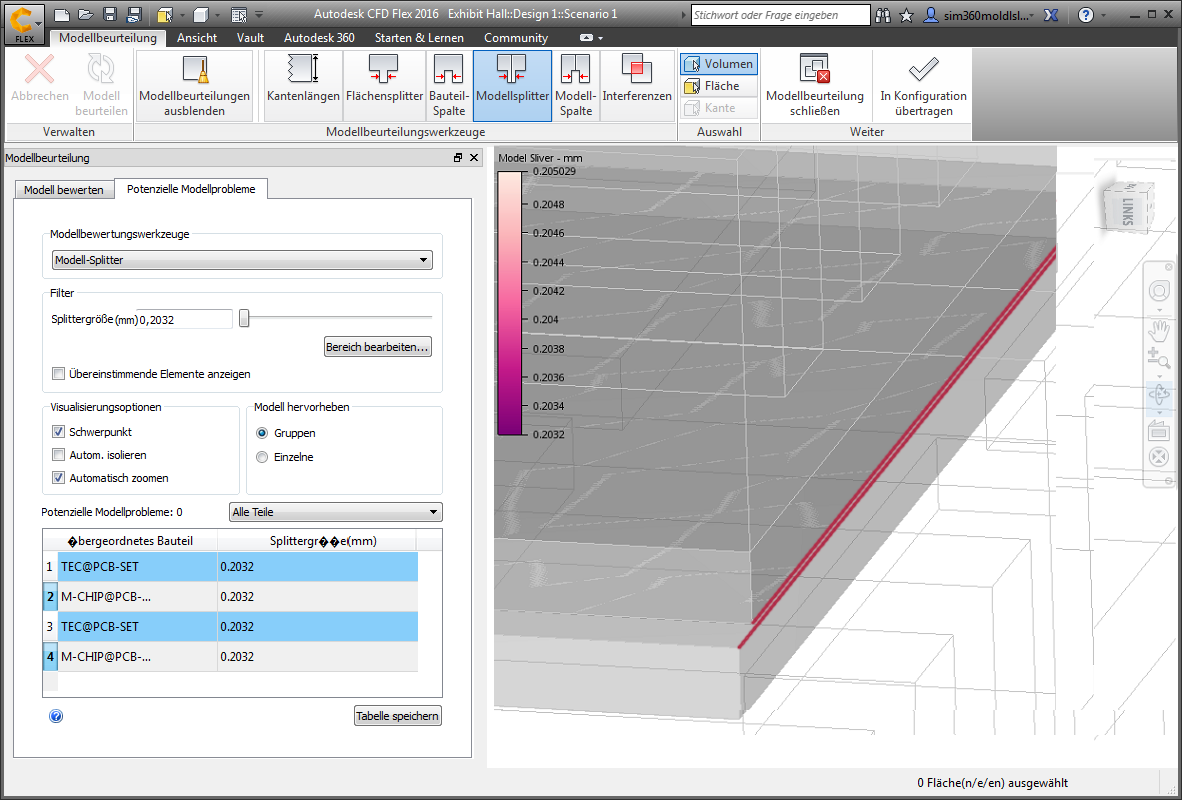

Durch Drehen und Zoomen der Ansicht können wir einen kleinen Abstand zwischen den Kanten der Kühlkörper und der Chips erkennen. Wenn Sie dieses Modell mit der aktuellen Konfiguration in CFD übertragen würden, würde dieser Kantenversatz zur Entstehung kleiner Splitterflächen führen.

In den meisten Fällen ist dieser kleine Versatz auf die falsche Verwendung von Baugruppenabhängigkeiten zurückzuführen. Um den kleinen Versatz an den Schnittstellen zu beseitigen, müssen wir folglich zu Inventor zurückkehren und die korrekten Abhängigkeiten anwenden.

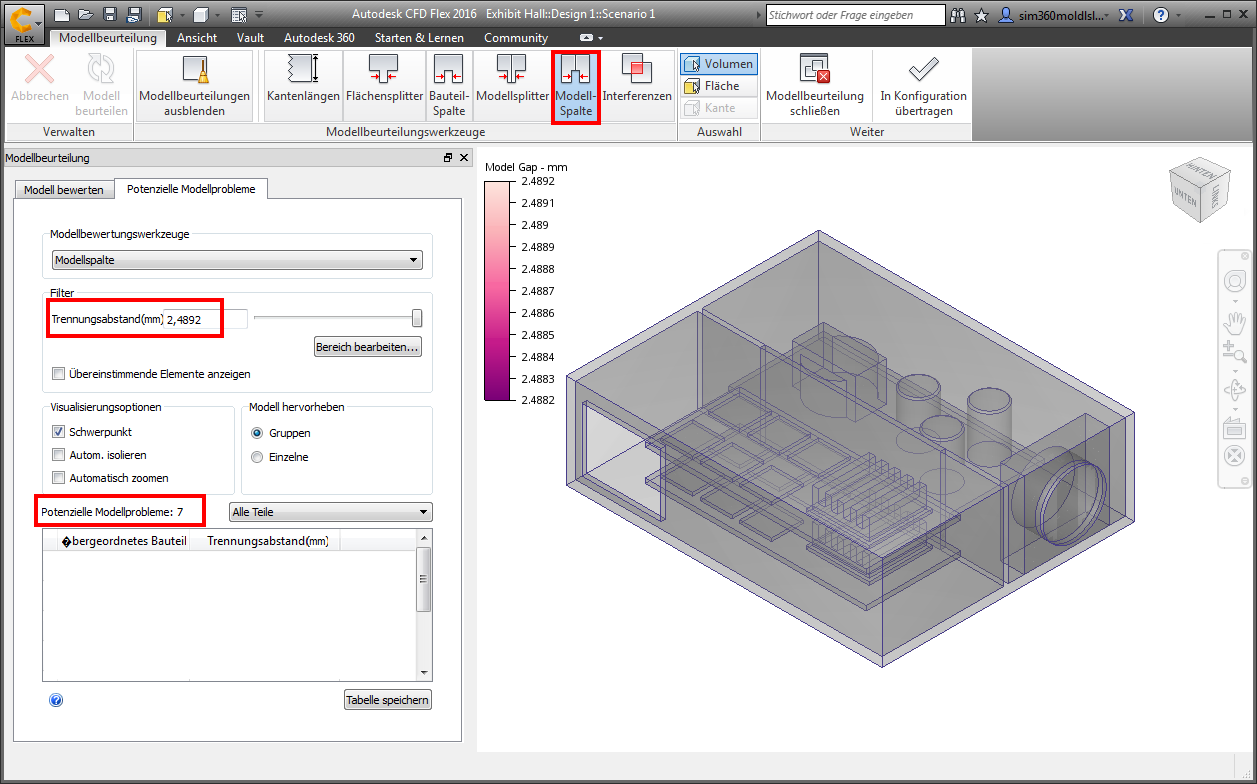

Modellspalten

Ähnlich wie Modell-Splitter können auch kleine Spalten zwischen Bauteilen Probleme in Bezug auf die Netzlängenskala verursachen. Verwenden Sie das Modellspalten-Werkzeug zur Prüfung Ihres Modells auf kleine Spalten, die dem CFD-Vernetzer Schwierigkeiten bereiten könnten.

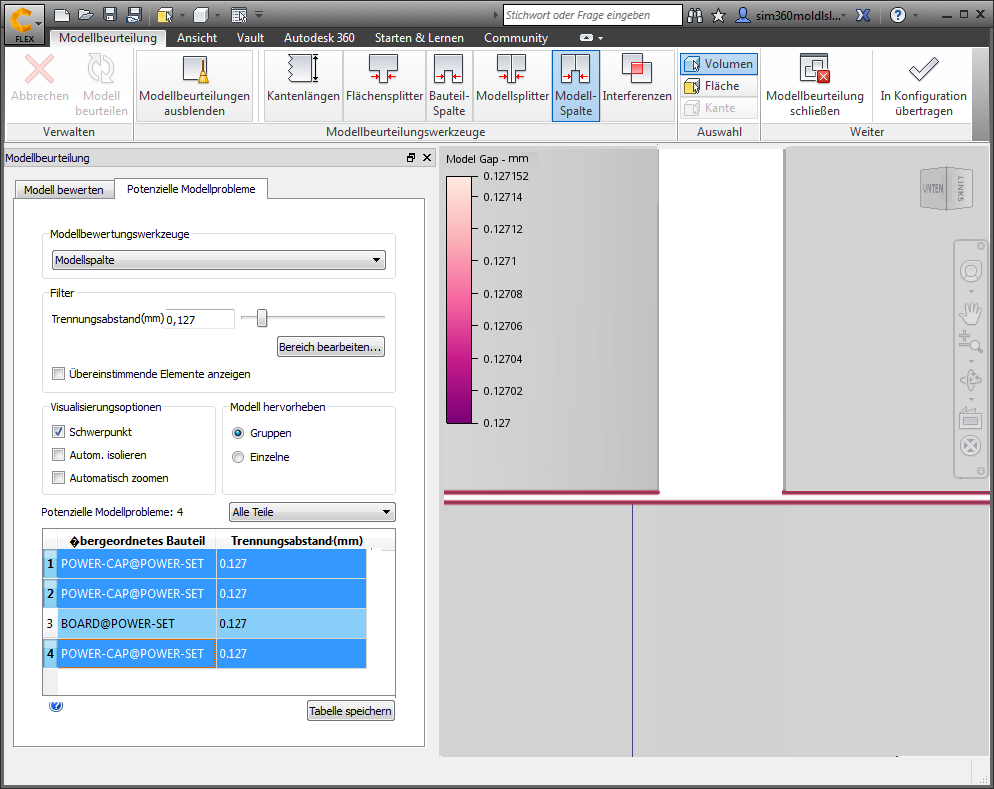

Kehren wir zu unserem Modell zurück und verwenden das Modellspalten-Werkzeug. Die Ausgangseinstellung für den Spaltengrößen-Filter beträgt vorgabemäßig 0.127 mm, was vier potenzielle Splitterprobleme liefert.

Durch Drehen und Zoomen der Ansicht können wir kleine Spalten zwischen den Kondensatoren und der Leiterplatte erkennen.

Diese Spalten sind ganz offensichtlich in unserem physischen Design nicht erwünscht und sollten vor der Übertragung des Modells in CFD beseitigt werden. Um die Spalten zwischen den Kondensatoren und der Leiterplatte zu beseitigen, müssen wir folglich zu Inventor zurückkehren und die korrekten Abhängigkeiten anwenden.

Interferenzen

Wenn aufgrund von Schnittstellen zwischen Bauteilen Interferenzen entstehen, können bei der Übertragung Ihres Modells in CFD unerwartete Ergebnisse auftreten. Aufgrund der beim Übertragen durchgeführten booleschen Operationen könnte Ihr Simulationsmodell zusätzliche Fluid-Bauteile oder Volumenkörper enthalten. Diese Bauteile können negative Auswirkungen auf Ihre Einrichtung und Vernetzungsvorgänge haben und zu Ineffizienzen beim Prozess, zu Vernetzungsfehlern und Ungenauigkeiten bei der Modellierung führen.

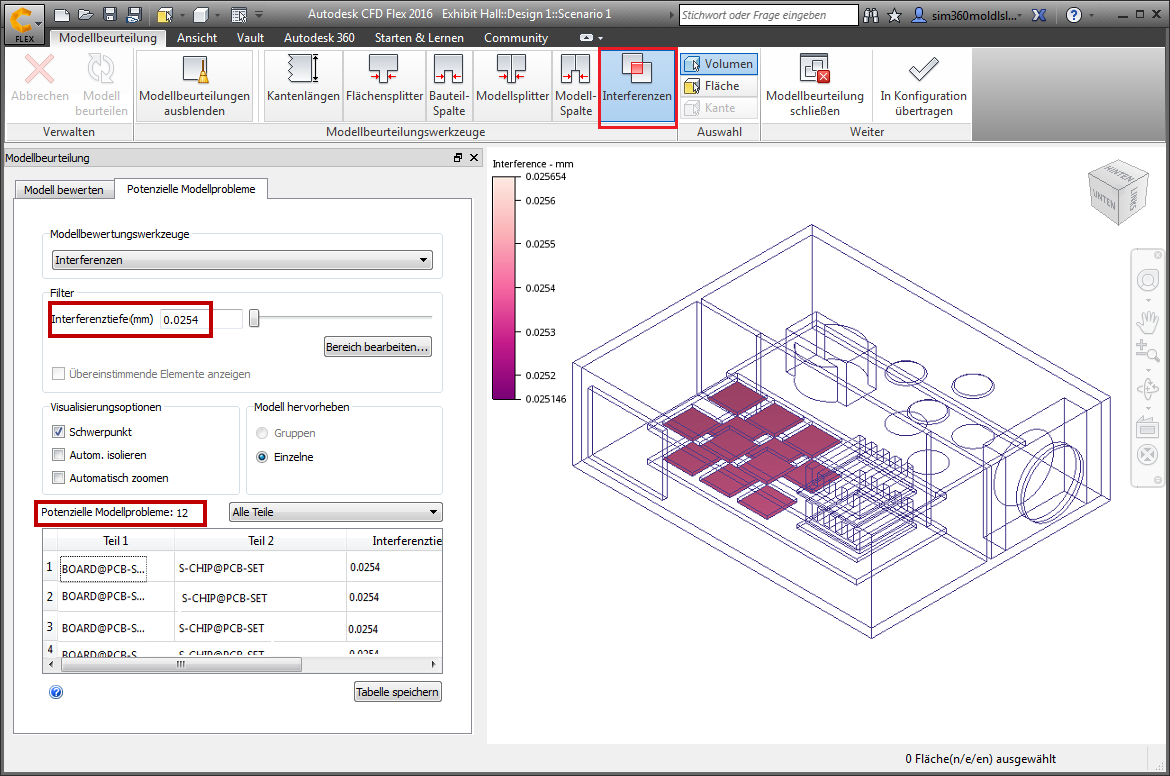

Kehren wir zu unserem Elektronikgehäuse-Baugruppenmodell zurück und verwenden das Interferenzen-Werkzeug. Wir konnten 12 Interferenzprobleme zwischen den Chips und Platinen finden.

Durch Drehen und Zoomen der Ansicht können wir Interferenzen erkennen, die dort entstehen, wo sich die führenden Kanten der Chips unterhalb der Platinenoberfläche erstrecken.

Wenn eine Interferenz klein genug ist, liegt sie möglicherweise noch im Toleranzbereich der CFD-Modellierung und wird während des Vernetzungsvorgangs beseitigt. Ist die Interferenz jedoch größer als der Toleranzbereich der Modellierungssoftware, kann Ihnen das erhebliche Probleme bereiten.

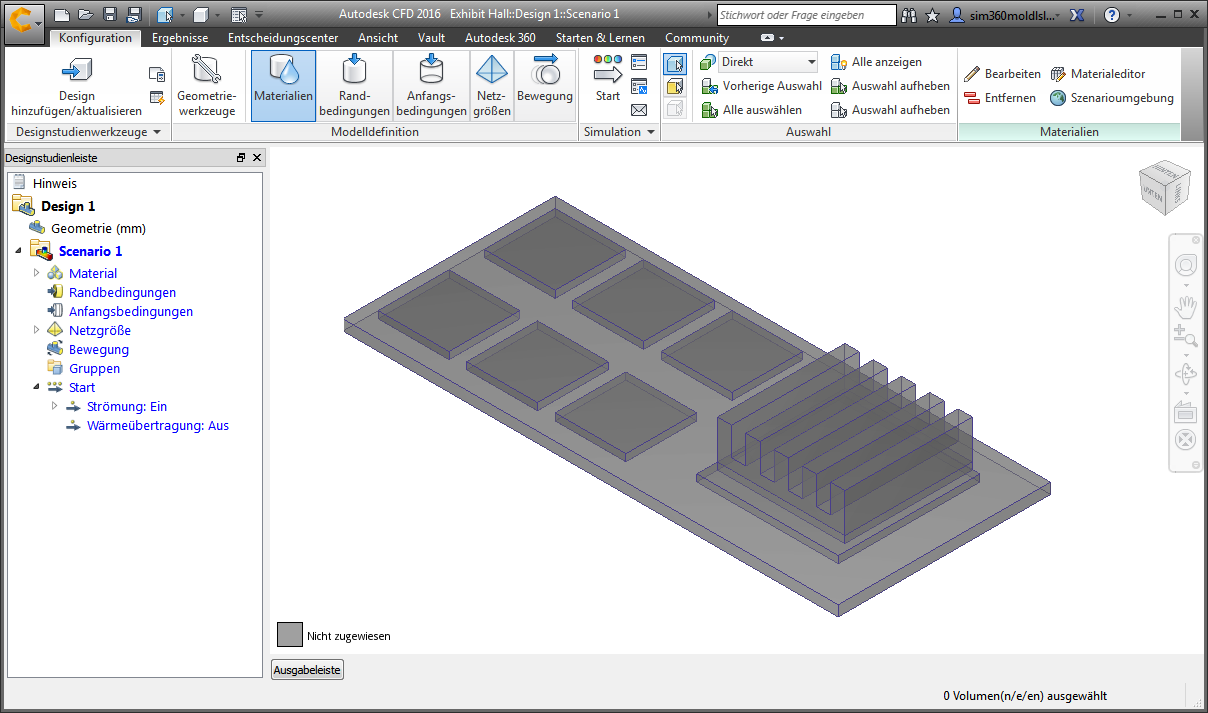

Wir haben das Modell mit den vorhandenen Interferenzen in CFD übertragen. Die folgende Abbildung zeigt eine der Leiterplattenbaugruppen (PCB). Wir wissen, dass zwischen den Chips und der Platine Interferenzen bestehen, doch in der Abbildung sind keine erkennbaren Probleme zu sehen.

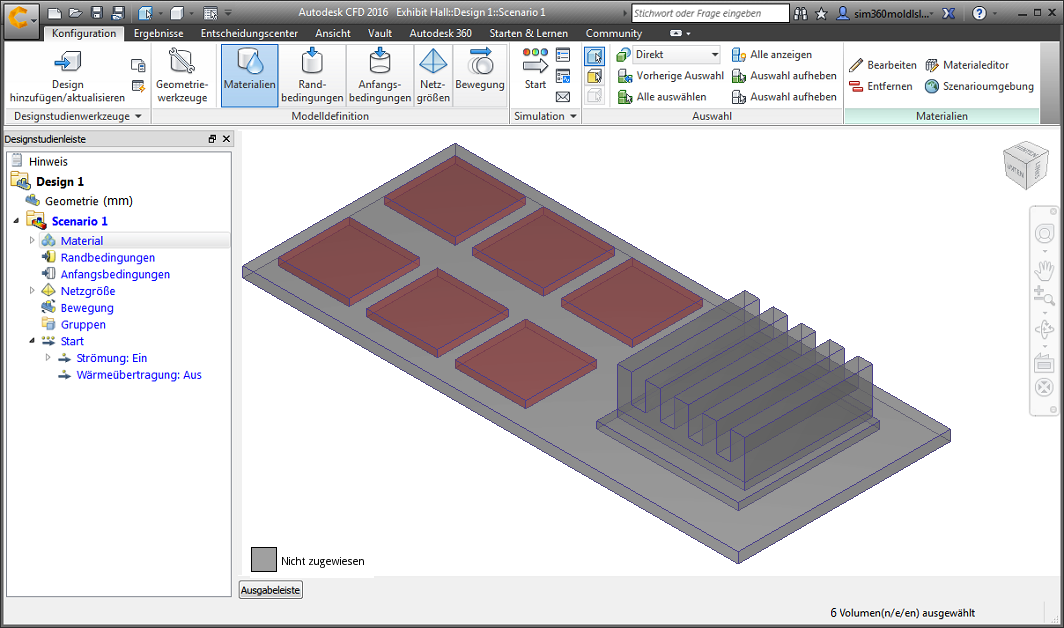

In der nächsten Abbildung wählen wir alle sechs Chips aus. Es sind immer noch keine Probleme zu sehen.

Sobald wir die Chips jedoch ausblenden, stellen wir etwas Interessantes fest. Die folgende Abbildung zeigt, dass die Interferenzen zwischen den Chips und der Platine in zusätzliche Chips umgewandelt wurden. Folglich haben wir nun 12 Chips pro Leiterplattenbaugruppe - sechs dünne, in die Platine integrierte Chips und sechs zusätzliche Chips, die auf diesen eingebauten Chips sitzen.

Diese Konfiguration der Chips ist in unserem physischen Design ganz offensichtlich nicht erwünscht. Folglich müssen wir zu Inventor zurückkehren und diese Interferenzen beseitigen, sodass wir letztendlich nur sechs auf der Leiterplatte sitzende Chips haben.

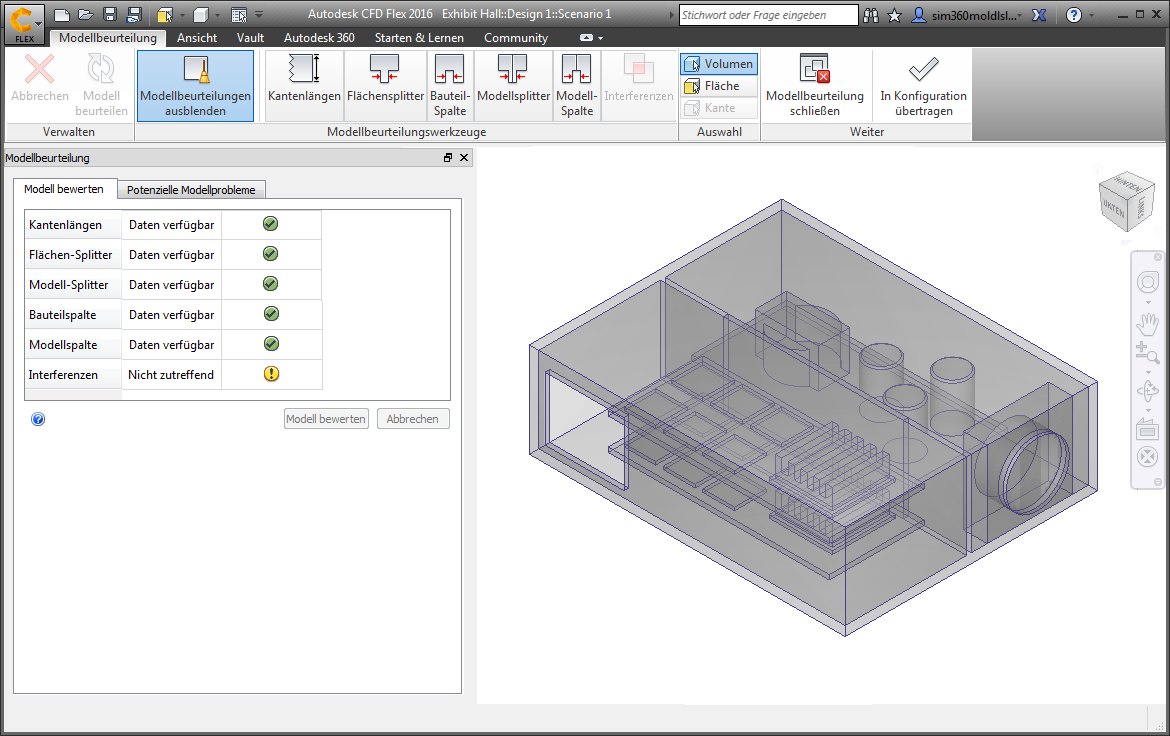

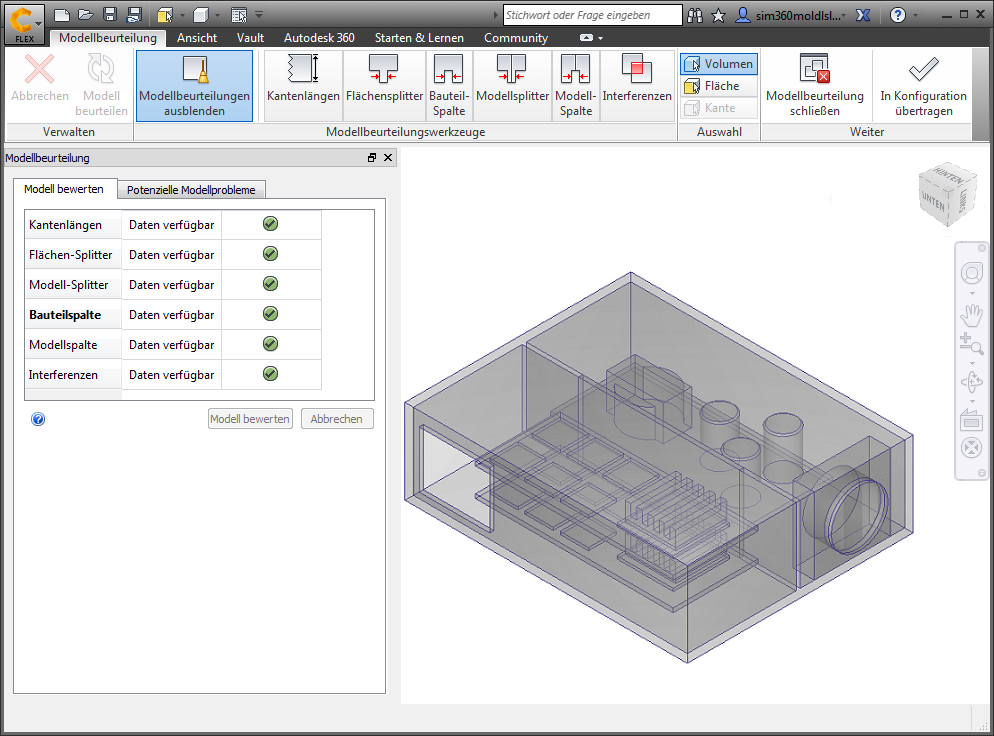

Überarbeitete Baugruppe

Bei der Rückkehr zu Inventor haben wir die Baugruppenabhängigkeiten aktualisiert, um sicherzustellen, dass:

- die Kühlkörper auf den Chips zentriert sind,

- die Kondensatoren die Leiterplatte berühren,

- die Chips die Platinen ohne Interferenzen berühren.