CAD モデルから CFD シミュレーションを設定する場合、さまざまなパーツやアセンブリのジオメトリの問題がメッシュの完成またはメッシュの品質に悪影響を及ぼす可能性があります。アセンブリの場合、MAT は 3 つのジオメトリの状況を評価し、結果のデータと設定を提供して調査を支援します。MAT とエンジニアリング上の判断を使用して、潜在的な問題の重要性を特定し、必要な解決方法を計画します。問題が見つかった場合は、CAD アプリケーションに戻り、ジオメトリを適切に修正します。

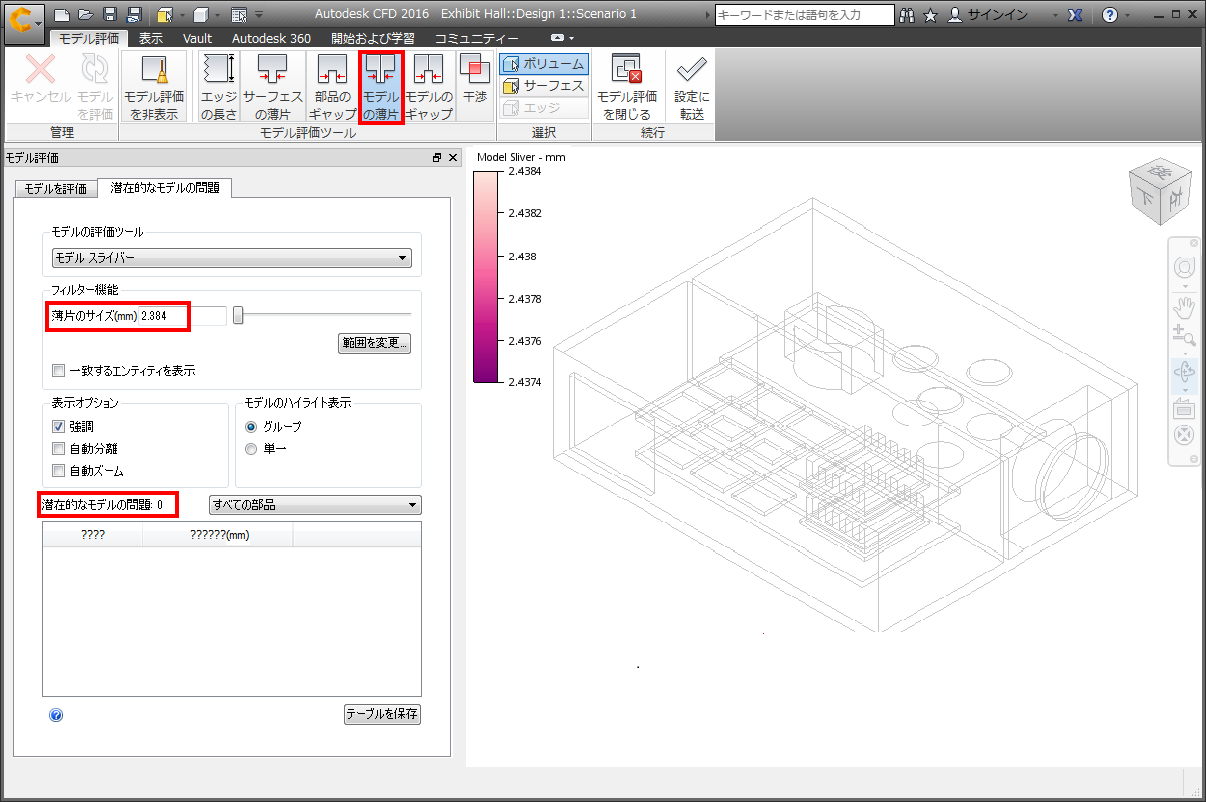

モデル スライバー

アセンブリのパーツは、スライバー サーフェスとも呼ばれる大きなアスペクト比のサーフェスが作成されるようにインタフェースされます。スライバー サーフェスには、メッシュ数を大幅に増やす細かいメッシュのシードが必要です。スライバー サーフェスには、解の精度に悪影響を及ぼすメッシュ長さスケールにおけるローカル不連続の挙動が発生することがあります。[モデル スライバー]ツールを使用してモデルを評価し、スライバー サーフェスの潜在的な問題があるかどうかを確認します。

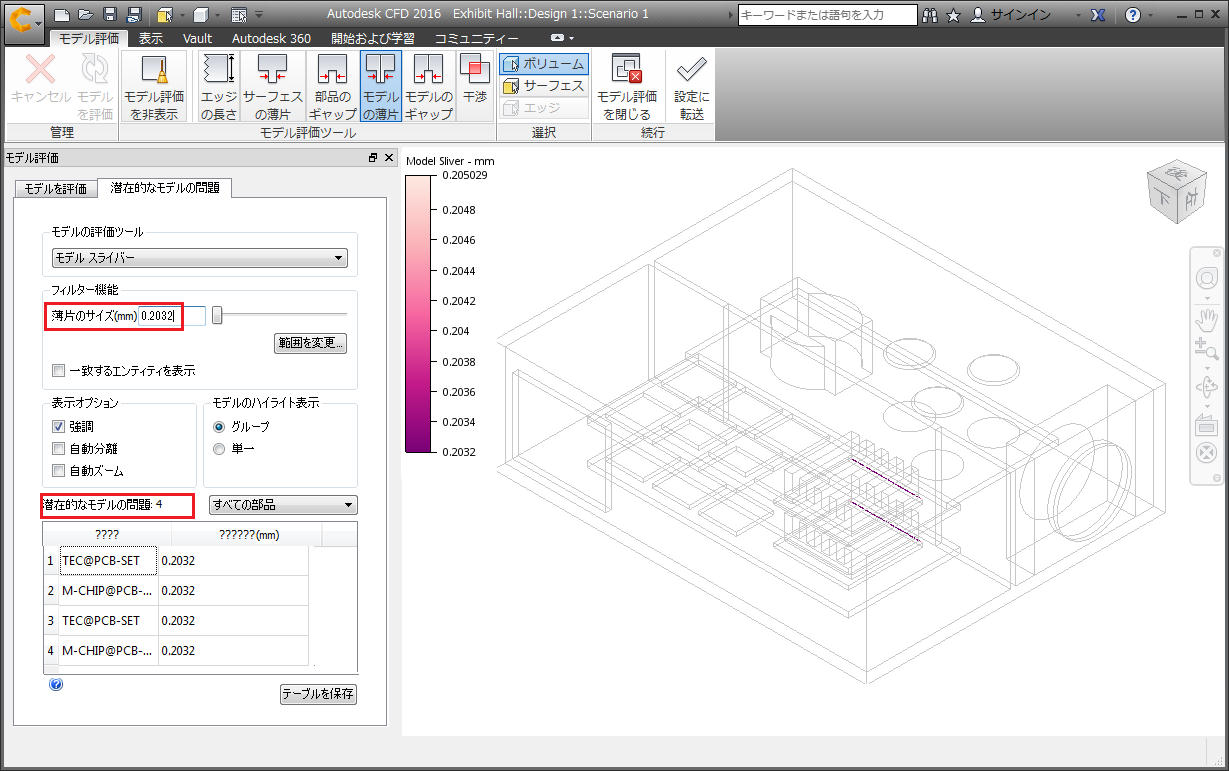

次の図に、[モデル スライバー]ツールを有効にした電子機器筐体のアセンブリ モデルを示します。スライバーの初期サイズのフィルタの既定値は 0.2032 mm に設定されるので、4 つの潜在的なスライバーの問題があります。

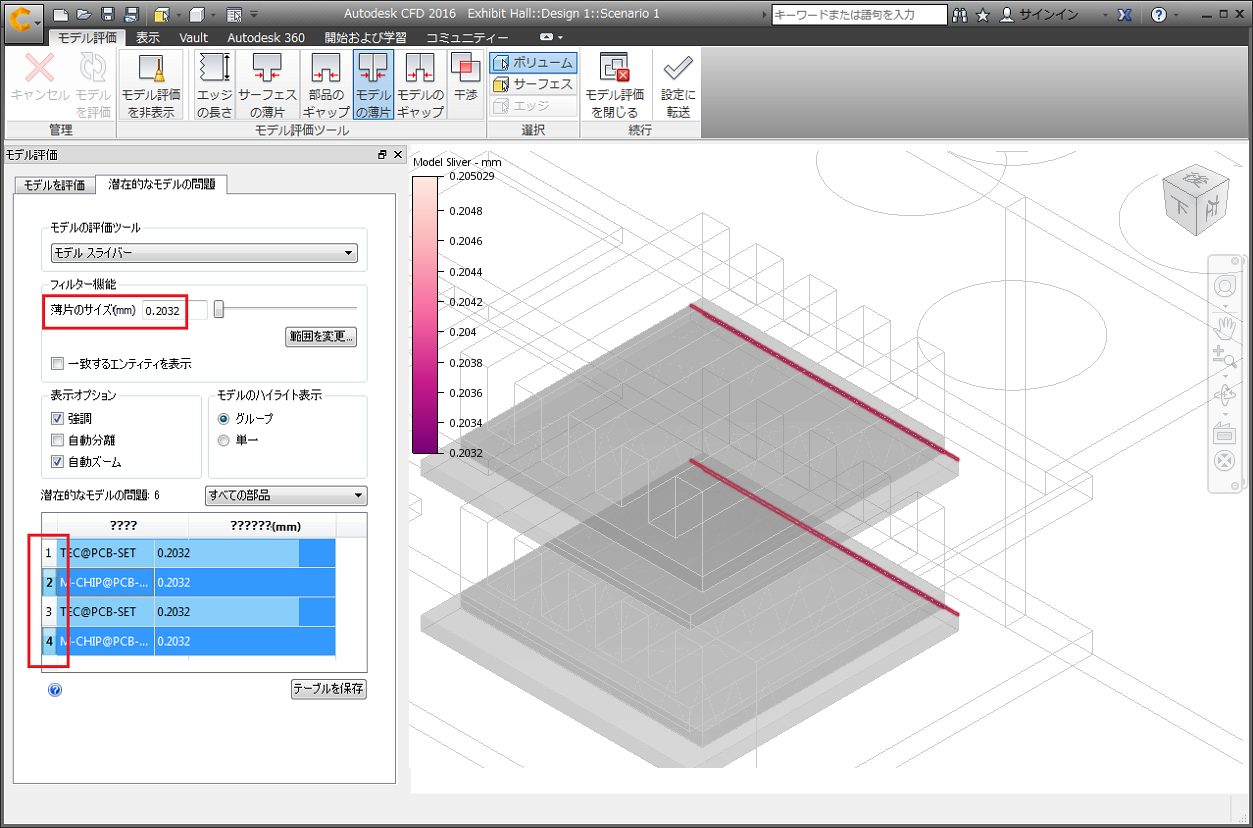

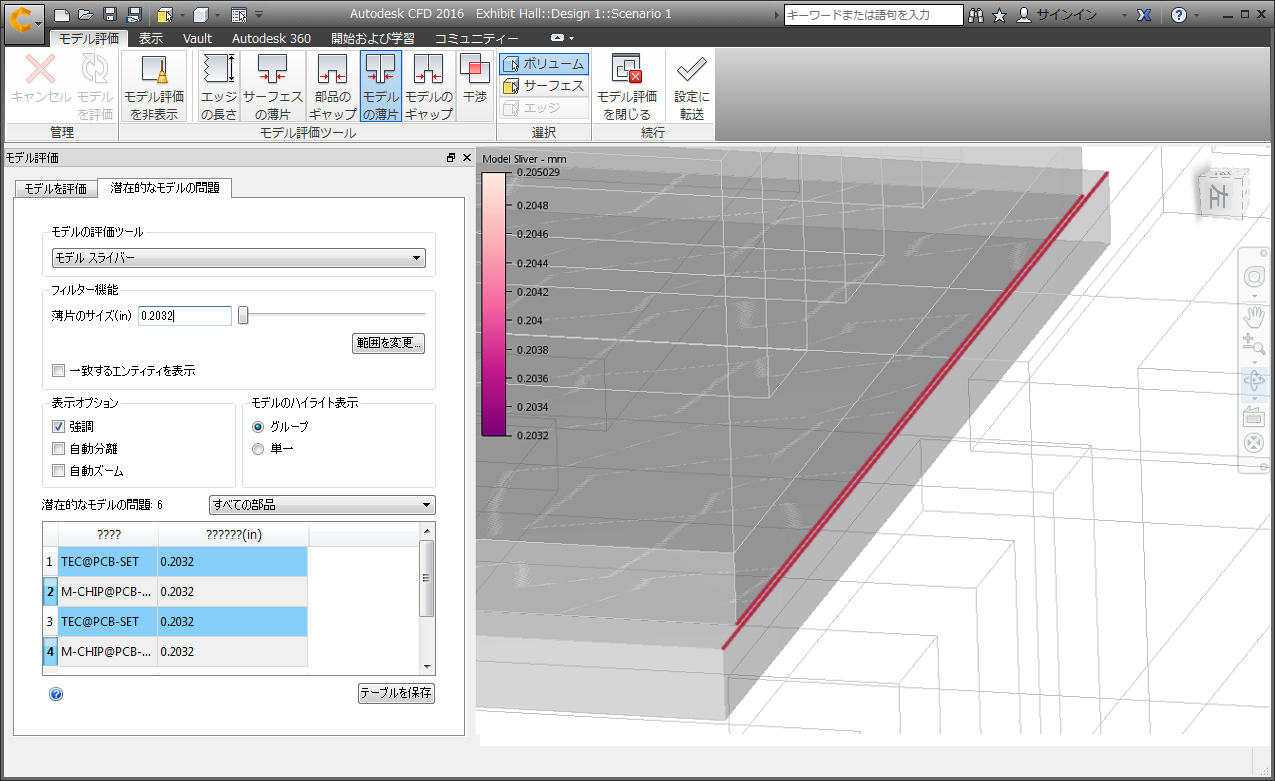

テーブル項目を選択し、[自動ズーム]と[強調]を選択すると、チップとヒート シンクのインタフェースに潜在的なスライバーの問題が表示されます。

ビューを回転およびズームすると、ヒート シンクとチップのエッジの間に小さなオフセットを確認できます。現在の設定でこのモデルを CFD に転送した場合、これらのオフセット エッジによって小さなスライバー サーフェスが形成されることがあります。

ほとんどの場合、この小さなオフセットは、アセンブリ拘束の不適切な適用の結果です。したがって、Inventor に戻って適切な拘束を適用し、インタフェースの小さなオフセットを排除します。

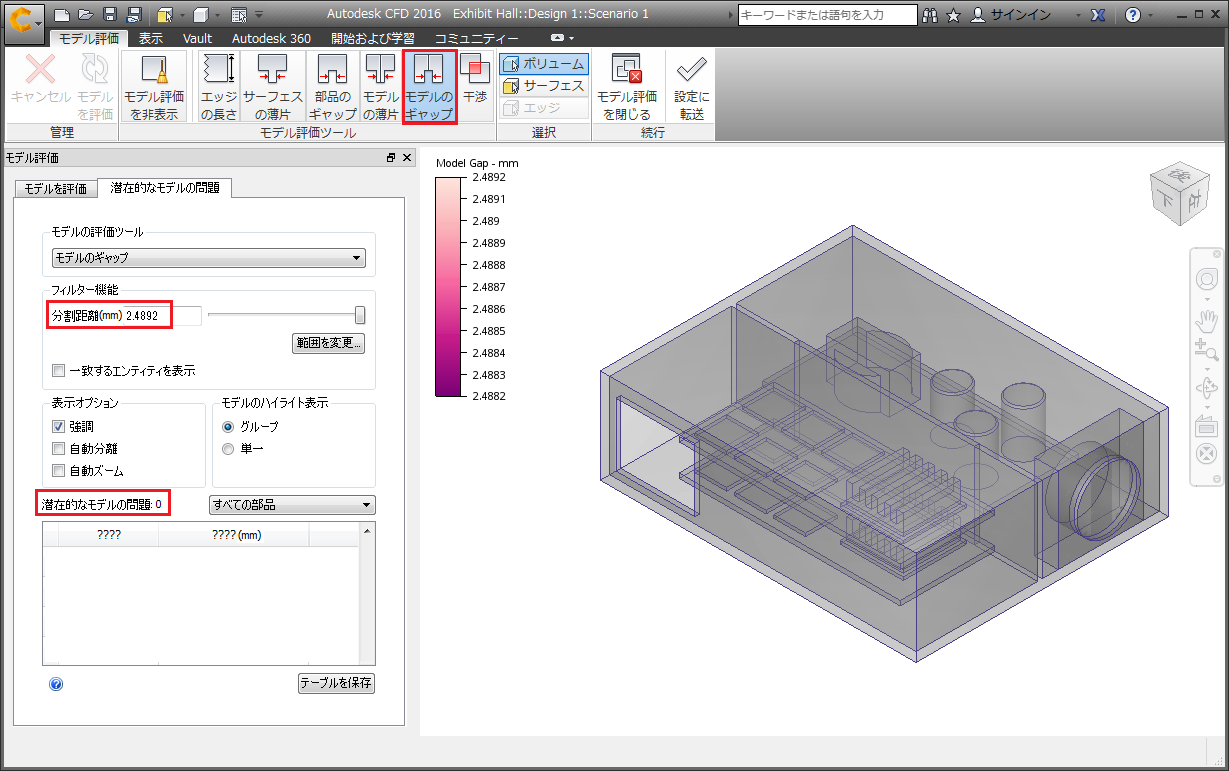

モデルのギャップ

モデル スライバーと同様に、アセンブリ パーツ間の小さなギャップによって、メッシュ長さのスケールの問題が発生することがあります。[モデルのギャップ]ツールを使用してモデルを評価し、CFD メッシャの問題の原因になる可能性がある小さなギャップがあるかどうかを確認します。

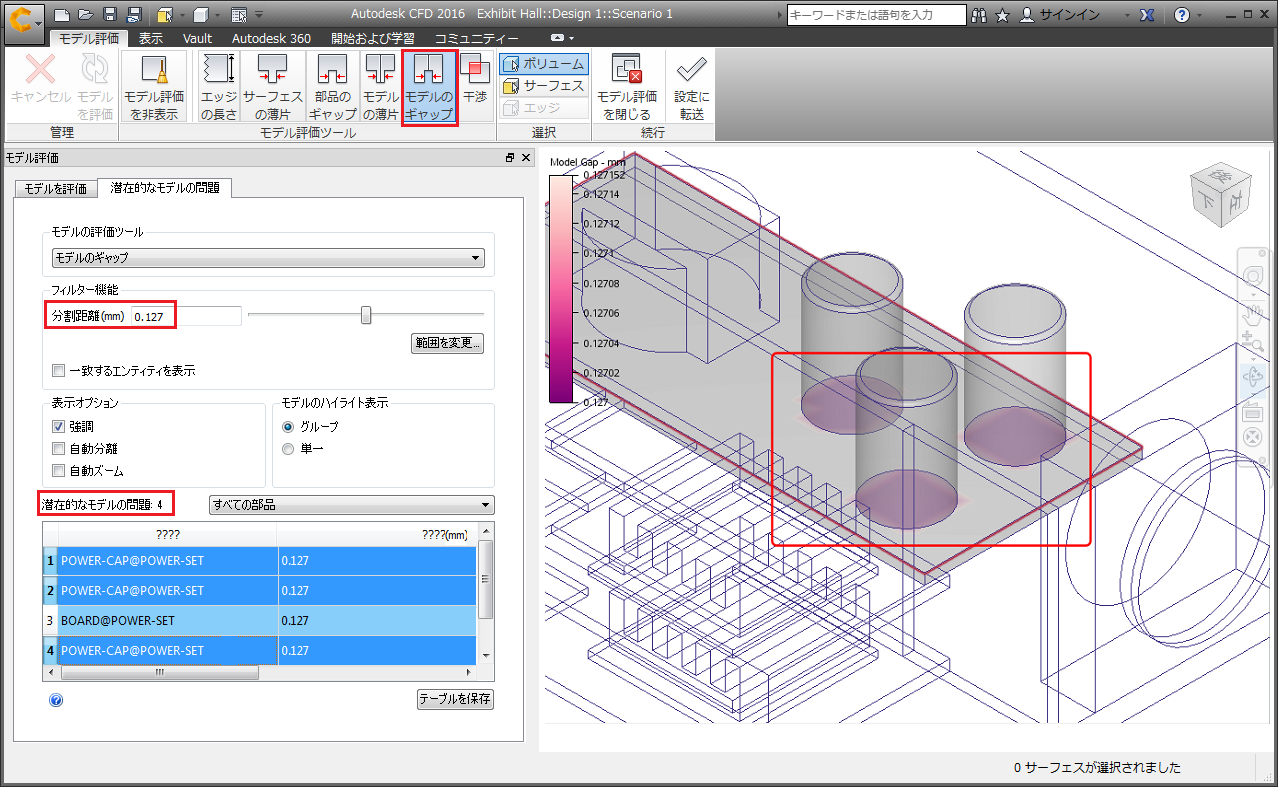

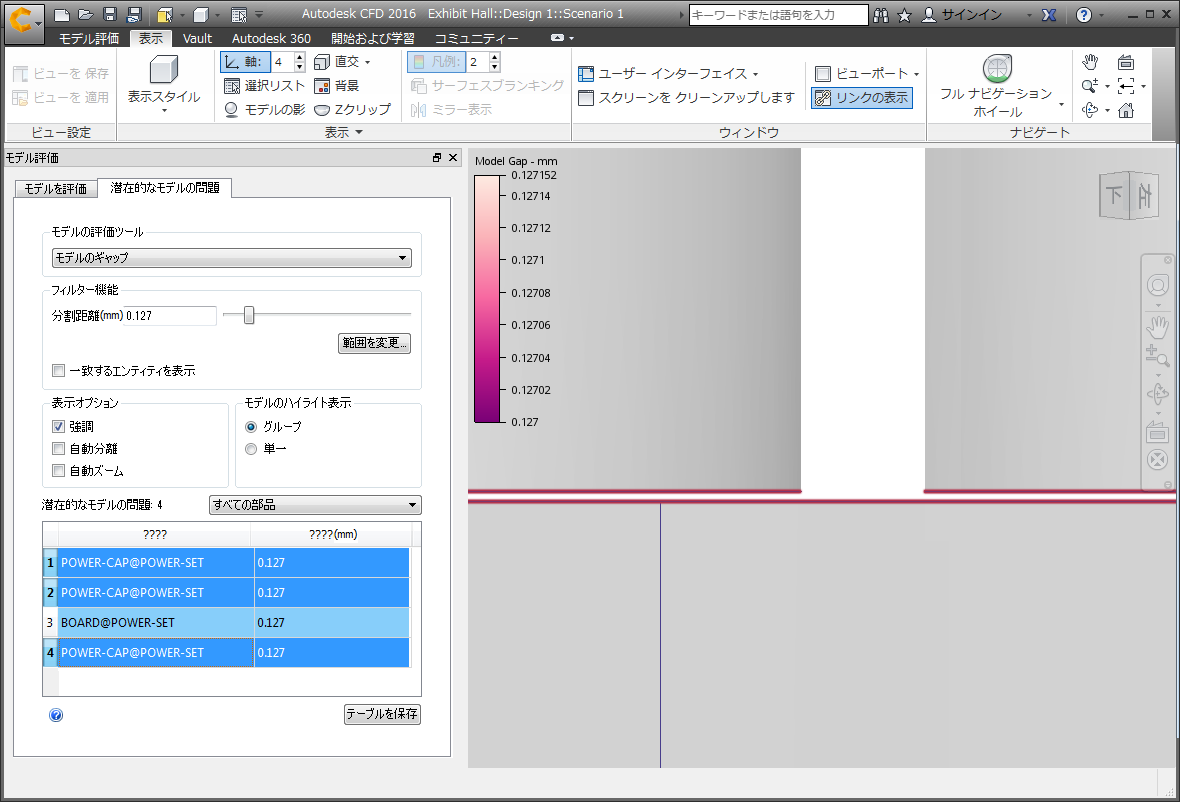

作成したモデルに戻って[モデルのギャップ]ツールを使用すると、初期フィルタのサイズ設定の既定値 0.127 mm によって、4 つの潜在的なギャップの問題が発生することがわかります。

ビューを回転およびズームすると、コンデンサと基板の間に小さなギャップがあることがわかります。

明らかに、これらのギャップは物理的な設計を反映したものではなく、モデルを CFD に転送する前に排除する必要があります。したがって、Inventor に戻って適切な拘束を適用し、コンデンサと基板の間の小さなギャップを排除します。

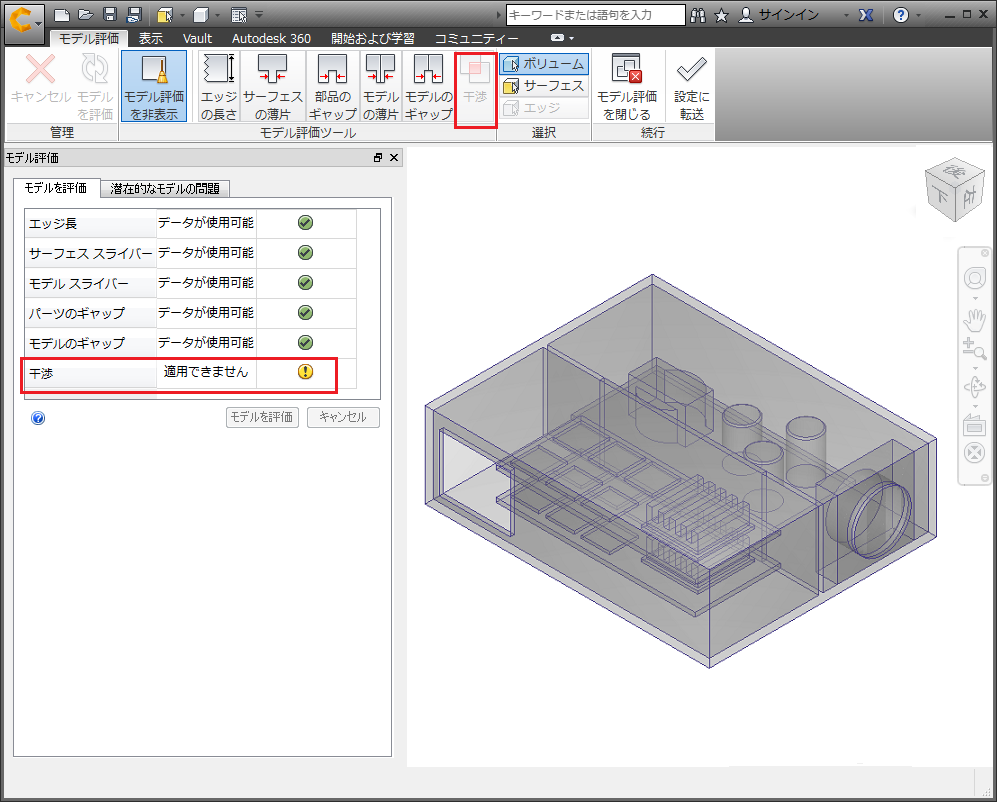

干渉

パーツ間のインタフェースによる干渉があると、モデルを CFD に転送する際に予期しない結果が発生することがあります。関連するブール演算によって、シミュレーション モデルに追加の流体または固体のパーツが必要になることがあります。これらのパーツは、設定およびメッシュ操作に影響を及ぼし、非効率的なプロセス、メッシュ生成エラー、不正確なモデリングにつながることがあります。

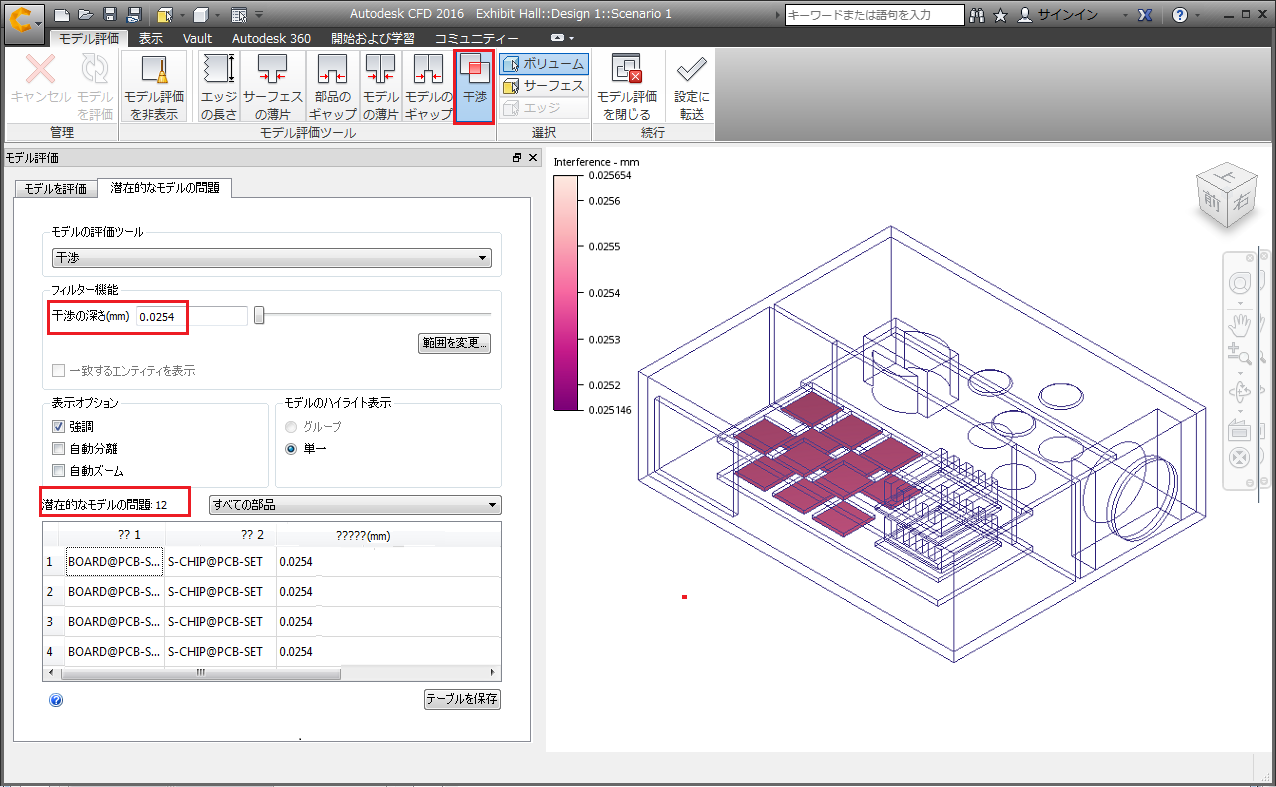

電子機器筐体のアセンブリ モデルに戻って[干渉]ツールを使用すると、チップと基板の間に 12 の干渉の問題が見つかります。

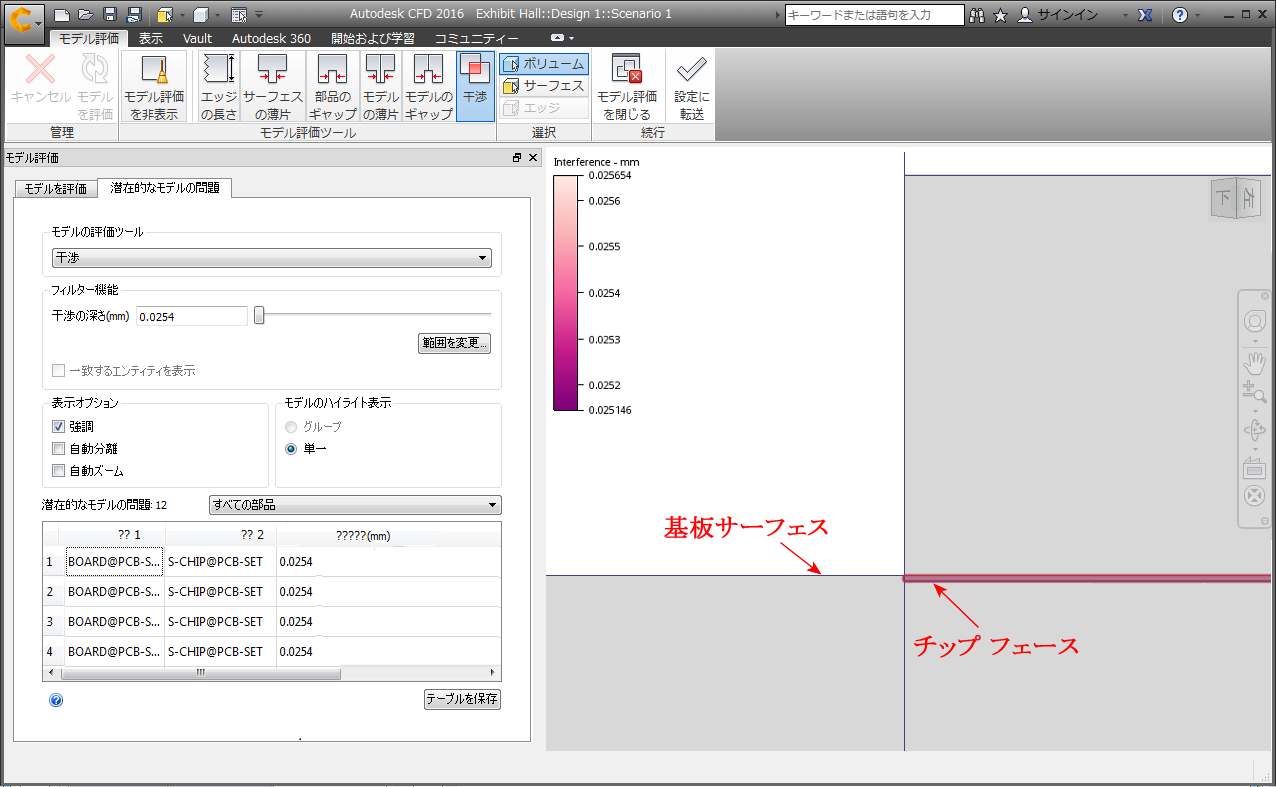

ビューを回転およびズームすると、チップの先端エッジが基板サーフェスの下に伸びている場所に干渉が発生していることがわかります。

干渉が十分に小さい場合は CFD モデリングの許容値内にあり、メッシュ処理中に排除されます。ただし、干渉がモデリングの許容値より大きい場合は、重大な問題が発生することがあります。

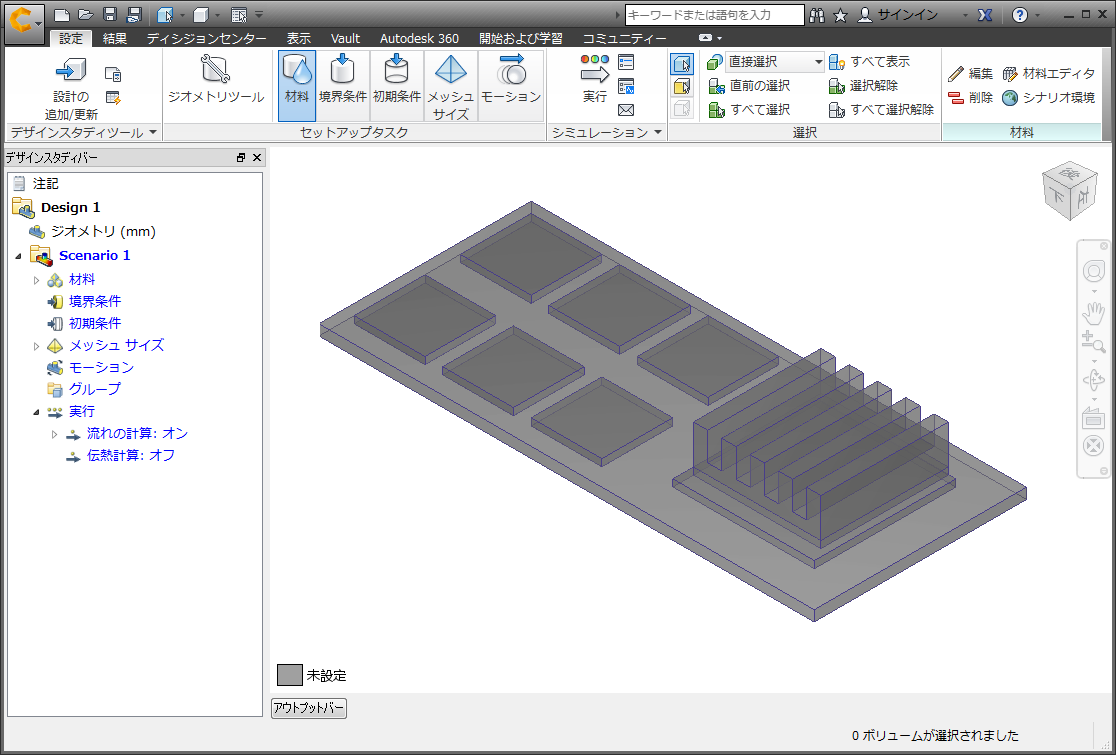

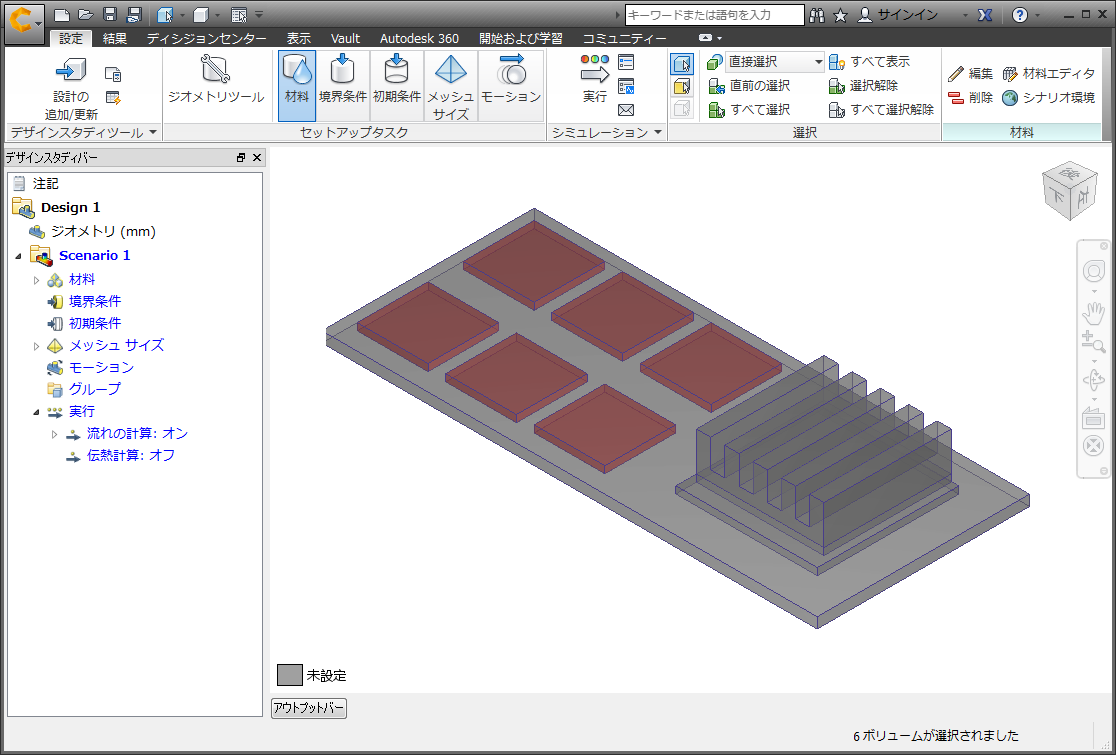

ここでは、干渉がある状態でモデルを CFD に転送します。次の図に、プリント基板(PCB)アセンブリの 1 つを示します。チップと基板の間に干渉があることがわかっていますが、この図に明らかな問題は示されていません。

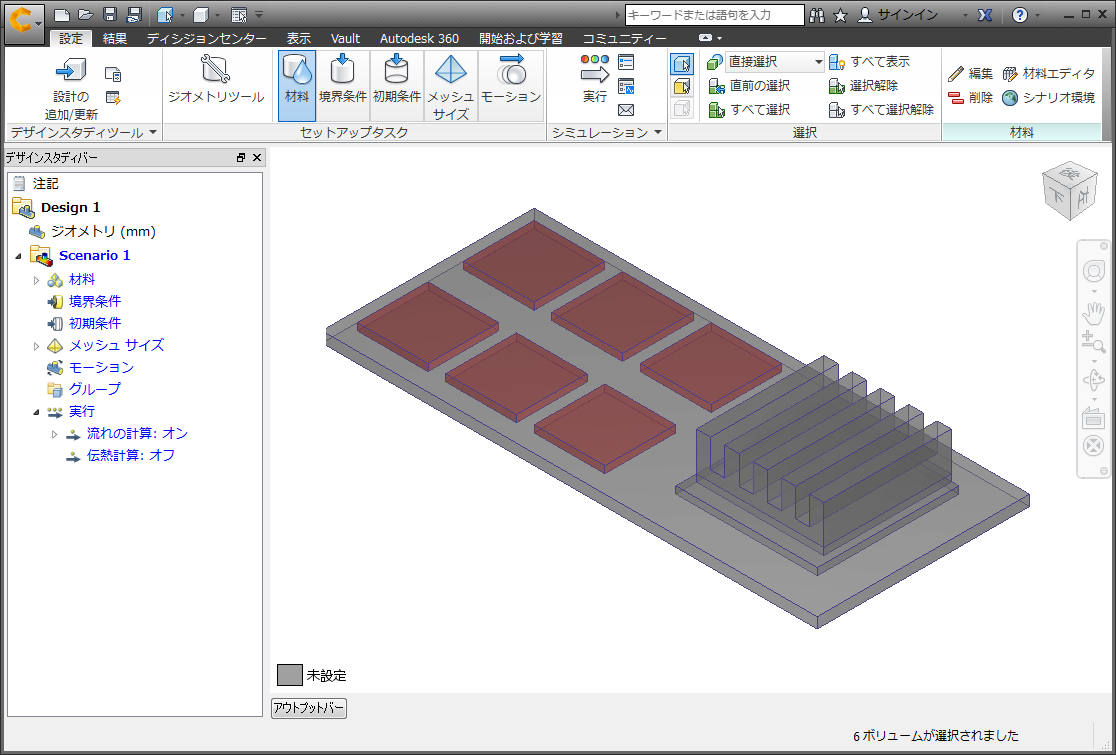

次の図では、6 つのすべてのチップが選択されています。ここでも、何も問題はないようです。

ただし、チップを非表示にすると、興味深いことがわかります。次の図では、チップと基板の間の干渉が追加のチップに変換されていることがわかります。ここでは、PCB アセンブリごとに 12 のチップがあります。これらの埋め込まれたチップの上に基板の埋め込まれた 6 つのシン チップがあります。

明らかに、このチップの構成は、物理的な設計を表していません。したがって、Inventor に戻って干渉を排除し、基板に 6 つのチップのみがマウントされるようにする必要があります。

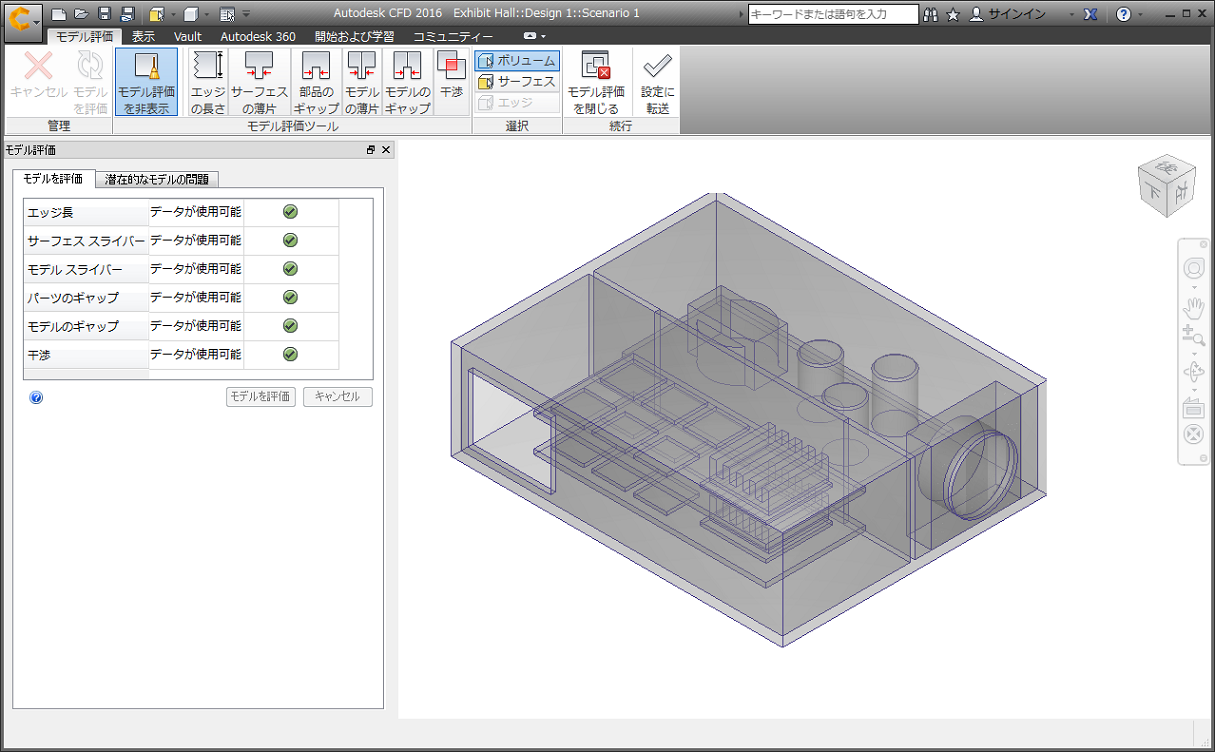

改訂されたアセンブリ

Inventor に戻り、次のようにアセンブリ拘束を更新しました。

- ヒート シンクはチップの中央に配置され、

- コンデンサが基板に接触し、

- チップは干渉なしに基板に接触している。