Design-Regeln

Fusion verwendet Design-Regeln, um die Anforderungen eines Designs zu definieren. Diese Regeln erstellen einen Satz von Anweisungen, die Fusion befolgt, damit Leiterplatten den Entwurfsstandards entsprechen. Leiterplatten werden anhand dieser Design-Regeln geprüft, jedoch werden Clearance-Fehler bei elektrisch irrelevanten Objekten (z. B. Rechtecke, Kreise und Texte) ignoriert, es sei denn, sie befinden sich auf Signal-Layern. Um zu überprüfen, ob Ihre Leiterplatte die Design-Regeln erfüllt, führen Sie nach dem Entwurf der Leiterplatte den Design Rule Check (DRC) aus. Dadurch werden etwaige Fehler erkannt.

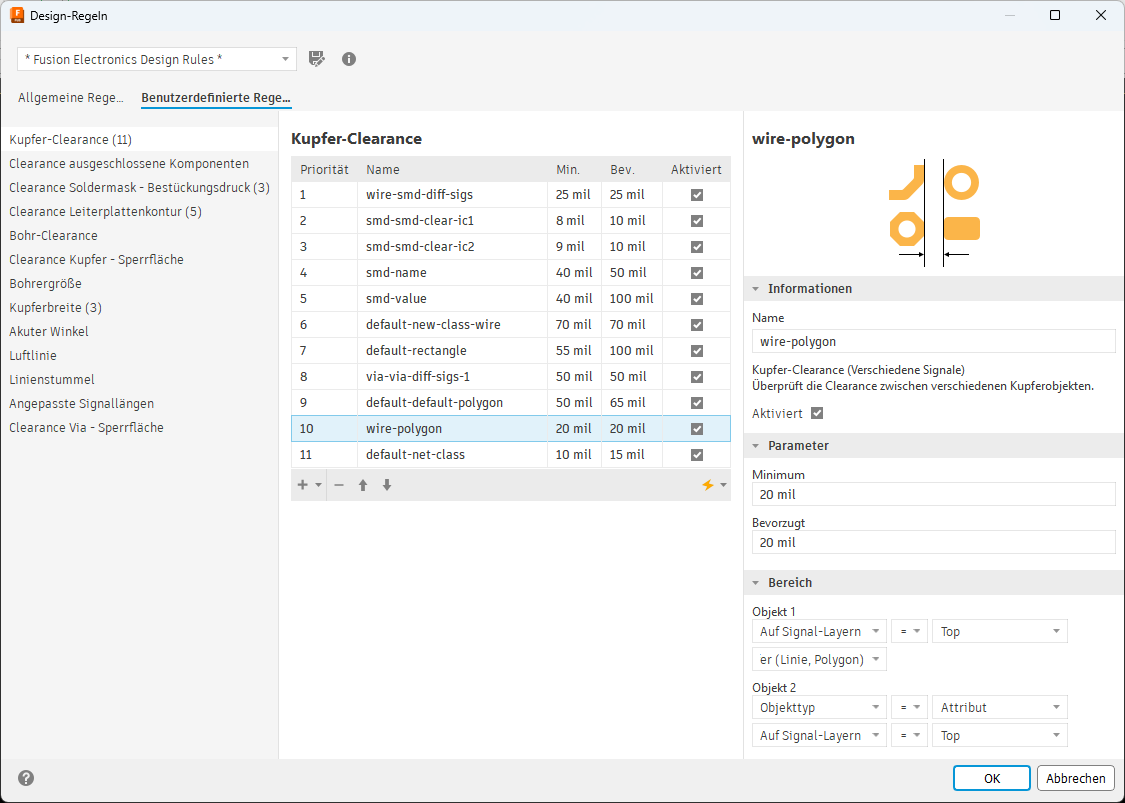

Fusion wendet Design-Regeln basierend auf ihren Prioritäten an und prüft bei Aufgaben wie dem manuellen Verlegen zuerst die höchste Priorität. Dazu gehört die Überprüfung auf Clearance, Kupferbreite oder Via-Bohrungsgröße. Legen Sie Regelprioritäten fest, um zuerst die strengsten Bereiche und dann die weniger strengen Bereiche zu überprüfen.

Erstellen Sie Leiterplattenentwürfe, die strenge Fertigungsanforderungen mit einem definierten Satz von Design-Regeln erfüllen. Richten Sie diese Regeln zu Beginn des Entwurfsprozesses ein, damit Sie sich auf den Entwurf konzentrieren können, ohne sich Gedanken über die Herstellbarkeit machen zu müssen. Passen Sie die Regeln in den Design-Regeln nach Bedarf an. Sie können die benutzerdefinierten Regeln als neue Fusion Electronic Design Rule-Datei (EDRU) unter einem neuen Namen speichern.

Die Funktion ZURÜCK/ZLÖSCH erfasst Änderungen an den Design-Regeln.

Design-Regelbereiche in interaktiven Arbeitsabläufen

Die folgenden interaktiven Arbeitsabläufe verwenden alle Design-Regeln, einschließlich der benutzerdefinierten:

Kupferflächen:

- Clearance-Berechnung: Verwendet den bevorzugten Wert der am besten anwendbaren Clearance-Regel.

Manuelle Verlegung:

- Clearance-Berechnung: Verwendet den bevorzugten Wert der am besten anwendbaren Clearance-Regel.

- Kupferbreite: Verwendet den bevorzugten Wert der am besten anwendbaren Regel für die Kupferbreite.

- Via-Bohrungsgröße: Verwendet den bevorzugten Wert der am besten anwendbaren Regel für die Bohrungsgröße.

Mehrfachverlegung:

- Clearance-Berechnung: Verwendet den bevorzugten Wert der am besten anwendbaren Clearance-Regel.

Differenzialpaar-Verlegung:

- Clearance-Berechnung: Verwendet den bevorzugten Wert der am besten anwendbaren Clearance-Regel.

Anmerkung: Die am besten anwendbare Regel ist die erste Regel, bei der Objekte den Bereichen Objekt 1 (alle Regeln) und Objekt 2 (nur binäre Regeln) entsprechen. Bei Regeln für Kupfer-Clearances mit gleichem Signal muss auch der Bereich Beide Objekte übereinstimmen.

Wenn Sie die automatische Vervollständigung verwenden, können Schnellverlegung, Mehrfachverlegung, Differenzialpaar-Verlegung und Mäander nur die folgenden signalbasierten Regelbereiche verwenden:

- In Netzklassen

- In Signal

- Ist Signal

- In Differenzialpaar

- In benannter Gruppe